# **R1610C** FAST ETHERNET RISC PROCESSOR

RDC RISC DSP Communication

RDC Semiconductor Co., Ltd

http://www.rdc.com.tw TEL: 886-3-666-2866 FAX: 886-3-563-1498

# CONTENTS

| 1. | Fea | atures                                                          | 7  |

|----|-----|-----------------------------------------------------------------|----|

| 2. | Blo | ock Diagram                                                     | 8  |

| 3. | Pin | Description                                                     | 9  |

|    | 3.1 | PIN Placement                                                   | 9  |

|    | 3.2 | Functional Description                                          |    |

|    | 3.3 | PIN Capacitance Description                                     | 17 |

|    | 3.4 | PIN Pull-up/Pull-down Description                               | 17 |

| 4. | Os  | cillator Characteristics                                        | 19 |

|    | 4.1 | Fundamental Mode                                                |    |

|    | 4.2 | Third-Overtone Mode                                             |    |

| 5. | Clo | ock Unit                                                        | 20 |

| 6. | Exe | ecution UNIT                                                    | 21 |

|    | 6.1 | General Registers                                               |    |

|    | 6.2 | Segment Registers                                               |    |

|    | 6.3 | Instruction Pointer and Status Flags Registers                  |    |

|    | 6.4 | Address Generation                                              |    |

| 7. | Per | ripheral Register List                                          | 24 |

|    | 7.1 | Legacy Peripheral Registers (Base Address FF00h)                | 24 |

|    | 7.2 | 16550 UART Register Definitions (Base Address FF00h)            |    |

|    | 7.3 | SDRAM Control Registers (Base Address FE00h)                    |    |

|    | 7.4 | Cache control register (Base Address FEC0h)                     | 25 |

|    | 7.5 | Fast Ethernet MAC Control Registers (Base Address: MAC / FE00h) |    |

| 8. | Per | ripheral Control Block Registers                                |    |

| 9. | Re  | set                                                             |    |

|    | 9.1 | Power-up Reset                                                  |    |

| 10. Bı  | Is Interface UNIT                                         | 32 |

|---------|-----------------------------------------------------------|----|

| 10.1    | Slow Bus and Memory Shadow                                |    |

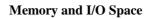

| 10.2    | Memory and I/O Interface                                  |    |

| 10.3    | Data Bus                                                  |    |

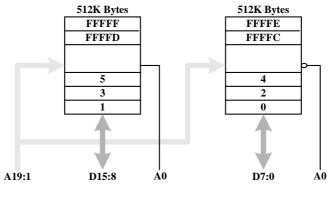

| 10.4    | Wait States                                               |    |

| 10.5    | Bus Width                                                 |    |

| 11. Ch  | nip Select UNIT                                           | 38 |

| 11.1    | UCS_n                                                     |    |

| 11.2    | PCSx_n                                                    |    |

| 12. Re  | efresh Control UNIT                                       | 42 |

| 13. Int | errupt Controller UNIT                                    | 43 |

| 13.1    | Interrupt Vector, Type and Priority                       | 44 |

| 13.2    | Interrupt Requests                                        |    |

| 13.3    | Programming the Registers                                 |    |

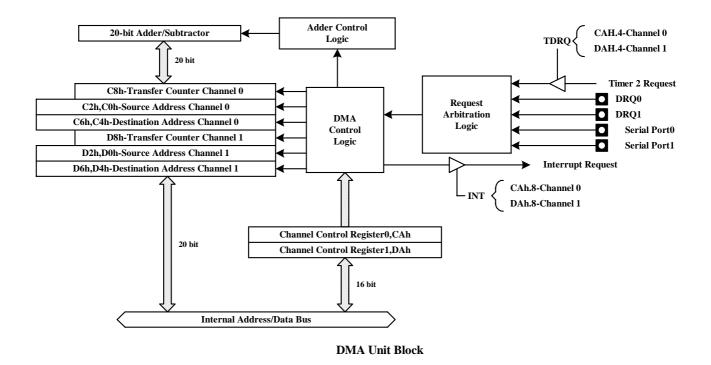

| 14. DN  | /A UNIT                                                   | 55 |

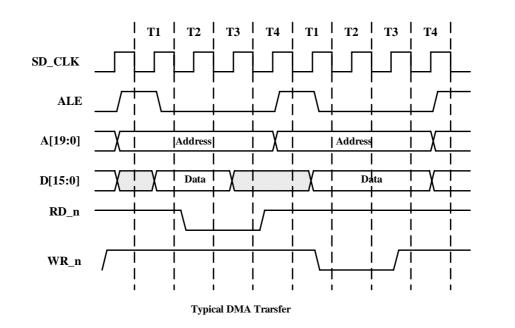

| 14.1    | DMA Operation                                             | 55 |

| 14.2    | External Requests                                         |    |

| 14.3    | Serial Port/DMA Transfer                                  |    |

| 15. Tir | mer Control UNIT                                          | 64 |

| 15.1    | Timer/Counter Unit Output Mode                            | 69 |

| 15.2    | Watchdog Timer                                            |    |

| 16. 16  | 550 UART Serial Port                                      | 72 |

| 16.1    | Receiver Buffer Register and Transmitter Holding Register |    |

| 16.2    | Divisor Latch LS and MS Register                          |    |

| 16.3    | Interrupt Enable Register                                 |    |

| 16.4    | Interrupt Identification Register                         |    |

| 16.5    | FIFO Control Register                                     |    |

| 16.6    | Line Control Register                                     |    |

| 16.7    | Modem Control Register                                    |    |

# R1610C Fast Ethernet RISC Processor

| 16.8    | Line Status Register                        | 80 |

|---------|---------------------------------------------|----|

| 16.9    | Modem Status Register                       |    |

| 16.10   | Scratchpad Register                         |    |

| 16.11   | Programmable Baud Generator                 |    |

| 16.12   | FIFO Interrupt Mode Operation               |    |

| 16.13   | FIFO Polled Mode Operation                  |    |

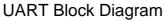

| 17. PIC | O UNIT                                      | 86 |

| 17.1    | PIO multi-function Pin list table           | 86 |

| 18. SD  | RAM Controller                              | 90 |

| 18.1    | SDRAM Mode Set Register                     |    |

| 18.2    | SDRAM Control Register                      |    |

| 18.3    | SDRAM Timing Parameter Register             |    |

| 19. CA  | CHE Controller                              | 92 |

| 19.1    | Cache Control Register                      |    |

| 19.2    | Non-Cache Region Register                   |    |

| 19.3    | Write Invalid Region Register               |    |

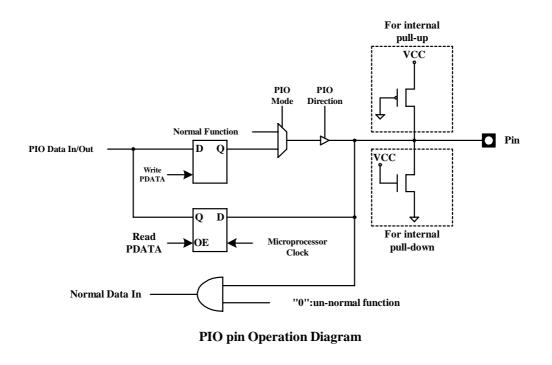

| 20. Fa  | st Ethernet Controller                      |    |

| 20.1    | RX Descriptor Format                        |    |

| 20.2    | TX Descriptor Format                        |    |

| 20.3    | MCR0: MAC Control Register 0 (00h)          |    |

| 20.4    | MCR1: MAC Control Register 1 (04h)          |    |

| 20.5    | MBCR: MAC Bus Control Register (08h)        |    |

| 20.6    | MTICR: TX Interrupt Control Register (0Ch)  |    |

| 20.7    | MRICR: RX Interrupt Control Register (10h)  |    |

| 20.8    | MTPR: TX Poll Command Register (14h)        |    |

| 20.9    | MRBSR: RX Buffer Size Register (18h)        |    |

| 20.10   | MRDCR: RX Descriptor Control Register (1Ah) |    |

| 20.11   | MLSR: MAC Last Status Register(1Ch)         |    |

| 20.12   | MMDIO: MDIO Control Register (20h)          |    |

| 20.13   | MMRD: MDIO Read Data Register (24h)         |    |

| 20.14   | MMWD: MDIO Write Data Register (28h)        |    |

| 20.15   | MTDSA0: TX Descriptor Start Address 0 (2Ch) |    |

|         |                                             |    |

# R1610C Fast Ethernet RISC Processor

| 20.16  | MTDSA1: TX Descriptor Start Address 1 (30h)        |     |

|--------|----------------------------------------------------|-----|

| 20.17  | MRDSA0: RX Descriptor Start Address 0 (34h)        | 115 |

| 20.18  | MRDSA1: RX Descriptor Start Address 1 (38h)        | 116 |

| 20.19  | MISR: INT Status Register (3Ch)                    |     |

| 20.20  | MIER: INT Enable Register (40h)                    | 117 |

| 20.21  | MECISR: Event Counter INT Status Register(44h)     | 117 |

| 20.22  | MECIER: Event Counter INT Enable Register (48h)    |     |

| 20.23  | MRCNT: Successfully Received Packet Counter (50h)  | 119 |

| 20.24  | MECNT0: Event Counter 0 (52H)                      |     |

| 20.25  | MECNT1: Event Counter 1 (54h)                      | 120 |

| 20.26  | MECNT2: Event Counter 2 (56h)                      | 120 |

| 20.27  | MCENT3: Event Counter 3 (58h)                      | 120 |

| 20.28  | MTCNT: Successfully Transmit Packet Counter (5Ah)  | 121 |

| 20.29  | MCENT4: Event Counter 4 (5Ch)                      | 121 |

| 20.30  | MPCNT: Pause Frame Counter (5Eh)                   |     |

| 20.31  | MAR0 ~3: Hash Table Word 0 ~3 (60h, 62h, 64h, 66h) |     |

| 20.32  | MID0 (68h, 6Ah, 6Ch)                               |     |

| 20.33  | MID1 (70h, 72h, 74h)                               |     |

| 20.34  | MID2 (78h, 7Ah, 7Ch)                               |     |

| 20.35  | MID3 (80h, 82h, 84h)                               |     |

| 21. DC | Electrical Characteristics                         | 128 |

| 21.1   | Absolute Maximum Ratings (25)                      |     |

| 21.2   | Operating Temperature                              |     |

| 22. AC | Electrical Characteristics                         |     |

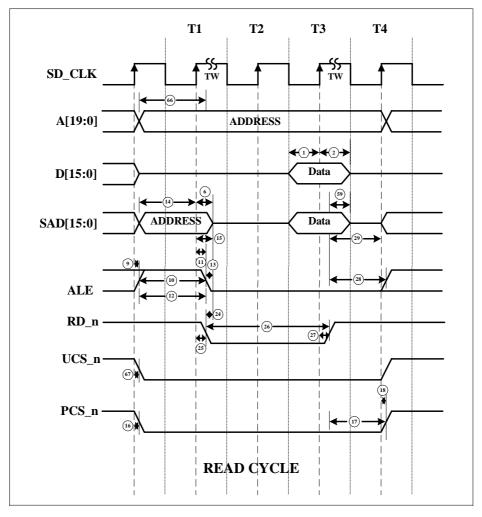

| 22.1   | Alphabetical Key to Switching Parameter Symbols    | 129 |

| 22.2   | Numerical Key to Switching Parameter Symbols       |     |

| 22.3   | CPU Bus                                            |     |

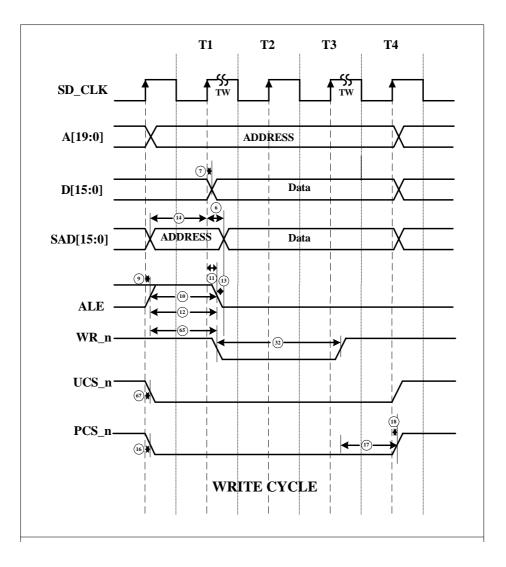

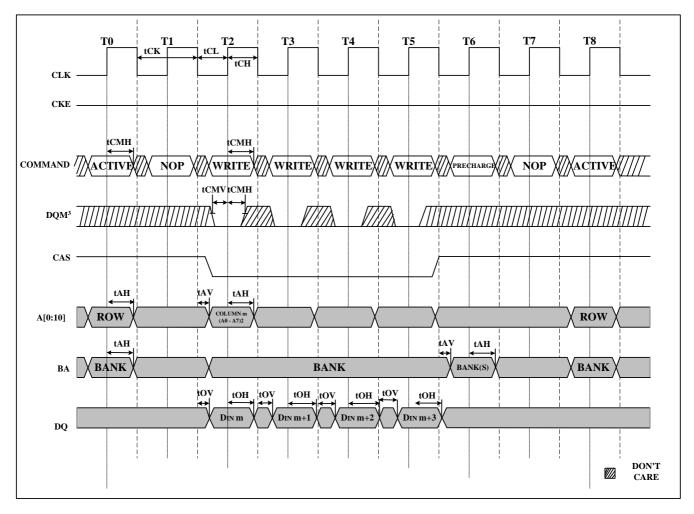

| 22.4   | SDRAM Bus                                          |     |

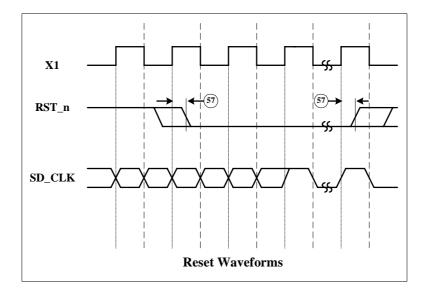

| 22.5   | CPU Reset                                          |     |

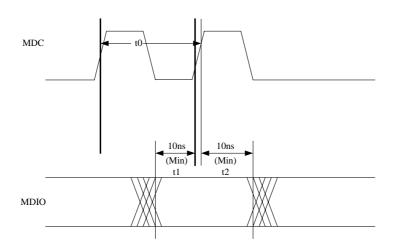

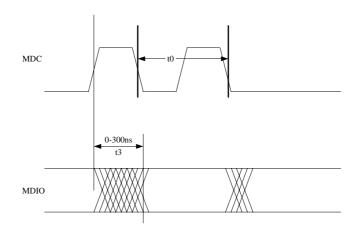

| 22.6   | MDC/MDIO Timing                                    |     |

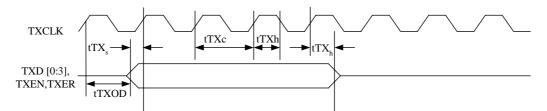

| 22.7   | TX Transmit Timing Parameters                      |     |

| 22.8   | TX Transmit Timing Diagram                         |     |

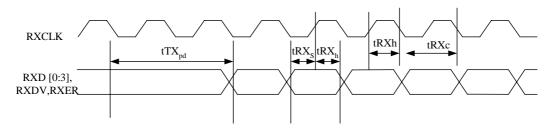

| 22.9   | RX Receive Timing Parameters                       |     |

|        |                                                    |     |

| 22.10  | RX Receive Timing Diagram                          |     |

| 23. Ins | struction Set OP-Code and Clock Cycles | .139 |

|---------|----------------------------------------|------|

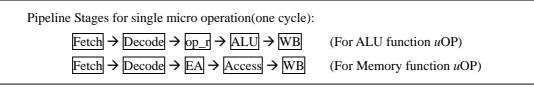

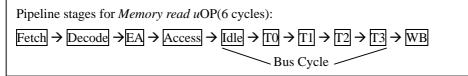

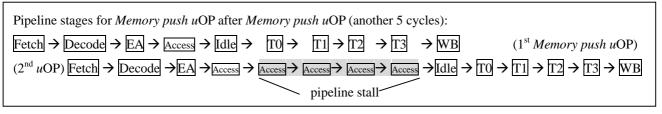

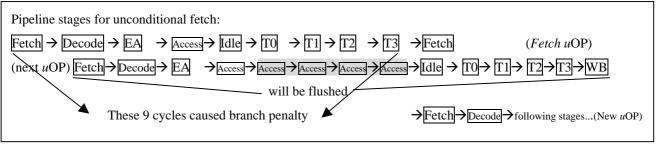

| 24. R1  | 610C Execution Timing                  | .143 |

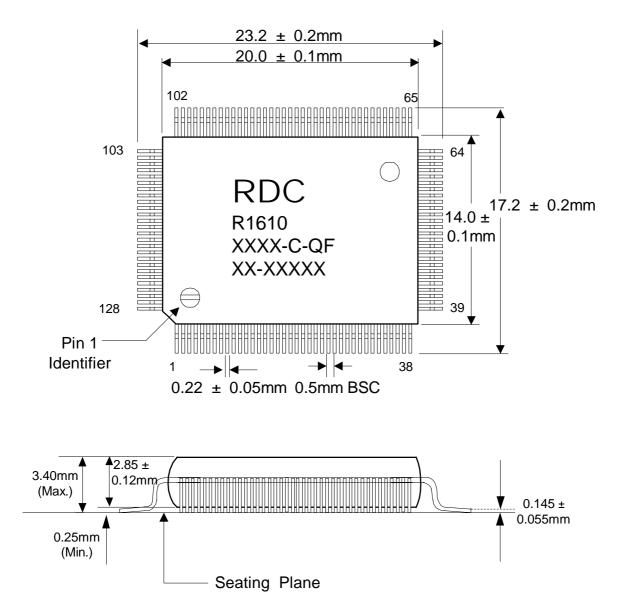

| 25. Pa  | ckage Information                      | .144 |

| 25.1    | PQFP 128 pins                          | 144  |

| 26. Re  | vision History                         | .145 |

# R1610C Fast Ethernet RISC Processor

#

# 1. Features

- Five-stage pipeline

- RISC architecture

- Bus interface

- Supports 16-bit data bus D [15:0]

- Supports non-multiplexed address bus A [19:0]

- 8-bit or 16-bit external bus dynamic access

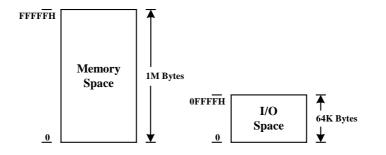

- 1M-byte memory address space

- 64K-byte I/O space

- Supports an independent data/address bus for external I/O device

- Supports a glue-less and simplified 16-bit PCMCIA bus interface

- Software is compatible with the 80C186 microprocessor

- Supports two 16550 UART serial channels with 16 bytes FIFO and hardware flow-control.

- Supports CPU ID

- Supports 18 PIO pins

- 16-bit SDRAM control Interface

- Three independent 16-bit timers and one independent programmable watchdog timer

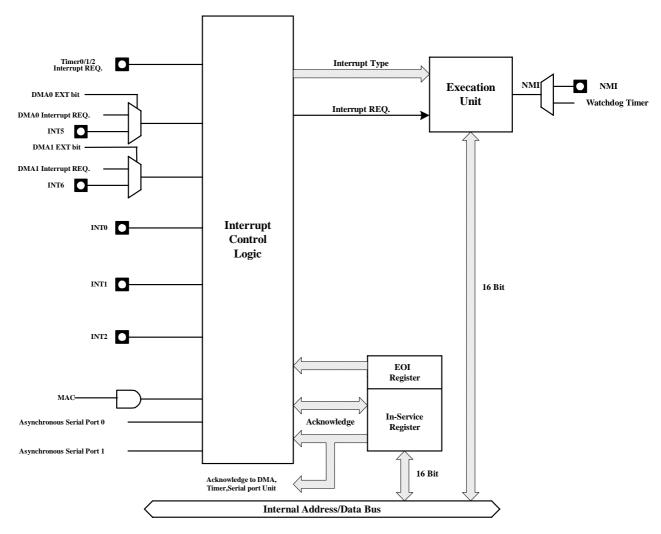

- The Interrupt controller with five maskable external interrupts and one non-maskable external interrupt

- Two independent DMA channels

- Programmable chip-select logic for Memory or I/O bus cycle decoder

- Programmable wait-state generator

- With 8-bit or 16-bit Boot ROM bus size

- 1-Port Fast Ethernet MAC with MII interface

- Supports an 8K-byte Uniform cache

- With 25MHz input frequency and up to 100MHz maximum internal frequency.

- Compatible with 3.3V I/O and 2.5V core voltage.

- Package Type includes 128-pin PQFP.

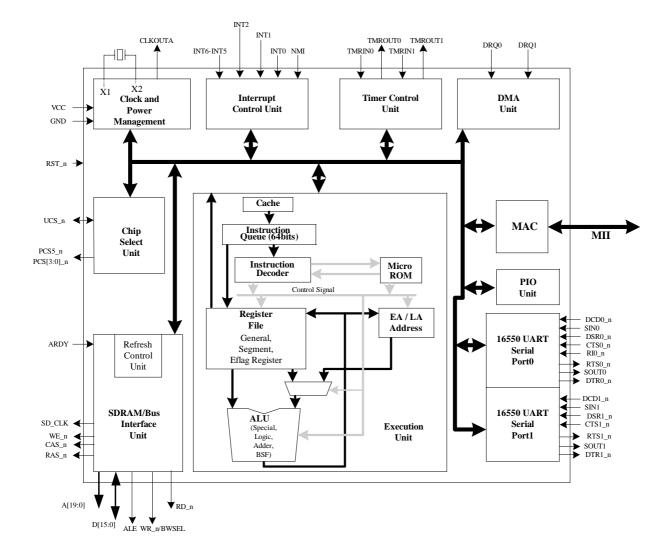

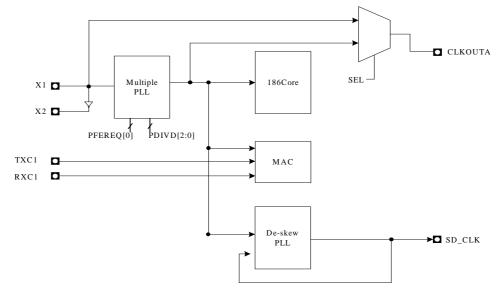

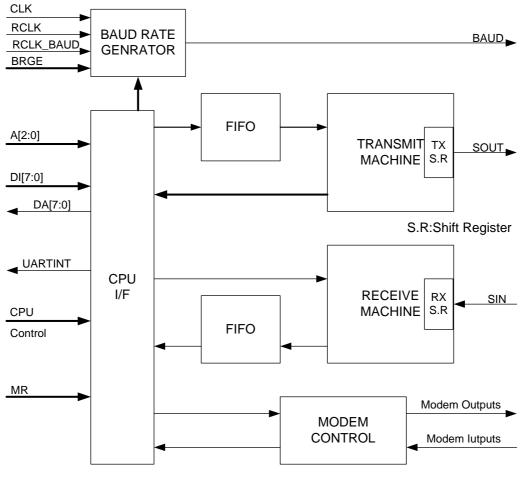

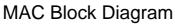

## 2. Block Diagram

## 3. Pin Description

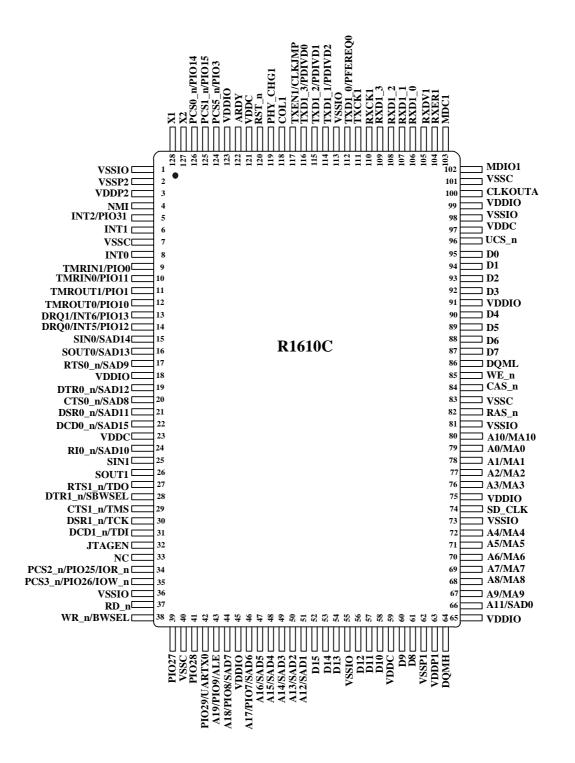

#### 3.1 PIN Placement

## 3.2 Functional Description

| I = Input;                                     |

|------------------------------------------------|

| O = Output;                                    |

| PU = Pull up 75K ;                             |

| PD = Pull down 75K ;                           |

| PU* = Pull up 75K when the PIOn pin is used;   |

| PD* = Pull down 75K when the PIOn pin is used; |

#### **CPU Core**

| PIN No. | Symbol  | Туре | Description                                                                                                                                                                                          |

|---------|---------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

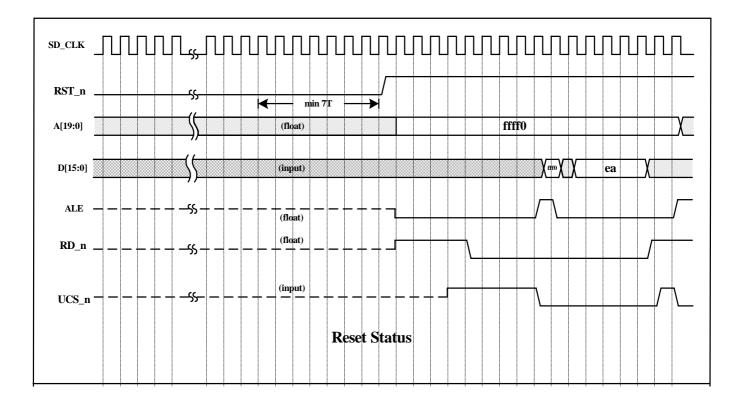

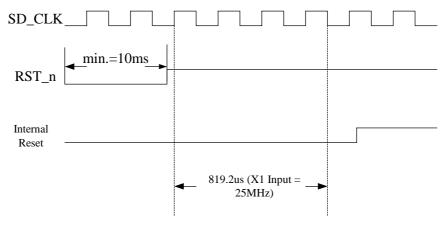

| 120     | RST_n   | I/PU | Reset input with schmitt trigger. When RST_n is asserted, the CPU immediately terminates all operations, clears the internal registers & logic, and changes the address to the reset address FFFF0h. |

| 128     | X1      | I    | 25MHz frequency input, within 100 ppm tolerance, to the amplifier (oscillator).                                                                                                                      |

| 127     | X2      | 0    | Frequency output from the inverting amplifier (oscillator).                                                                                                                                          |

| 100     | CLKOUTA | 0    | The CLKOUTA output frequency is the same as the X1 input frequency.<br>When high, the CLKOUTA is from Multiple-PLL. When low, the CLKOUTA is from X1.                                                |

| Bus Interface |            |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|---------------|------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| PIN No.       | Symbol     | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| 37            | RD_n       | ο    | Read Strobe. One active low signal indicates that the microcontroller is performing a memory or I/O read cycle. The RD_n floats during a bus hold or reset.                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| 38            | WR_n/BWSEL | O/PU | <ul> <li>Write strobe. This pin indicates that the data on the bus is to be written into a memory or an I/O device. WR_n is active during T2, T3, and Tw of any write cycle, floating during a bus hold or reset.</li> <li>BWSEL is used to decide the boot ROM bus width when RST_n goes from low to high.</li> <li>If BWSEL is with an external pull-low resistor (4.7k ohm), the boot ROM bus width is 8 bits. Otherwise the boot ROM width is 16 bits.</li> </ul>                                                                                             |  |

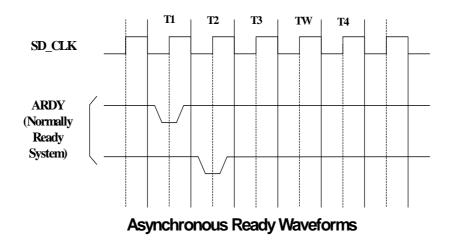

| 122           | ARDY       | I/PU | Asynchronous ready. This pin indicates to the microcontroller that the addressed memory space or I/O device will complete a data transfer. The ARDY pin accepts a rising edge of input that is asynchronous to SD_CLK and is active high. However, the falling edge of ARDY must be synchronized to SD_CLK. Tie ARDY high, so the microcontroller is always asserted in the ready condition. To guarantee the wait states inserted, ARDY must be pulled low before to phase 2 of T2 or phase 1 of T3. Please note that the ARDY signal is internally pulled high. |  |

| FIN NU.     | Symbol         | Type | Upper memory chip select For LICS n, this pin is active low                                                               |

|-------------|----------------|------|---------------------------------------------------------------------------------------------------------------------------|

| PIN No.     | Symbol         | Туре | Description                                                                                                               |

| Chip Select | Unit Interface |      |                                                                                                                           |

| 52          | D15            |      |                                                                                                                           |

| 53          | D14            |      |                                                                                                                           |

| 54          | D13            |      |                                                                                                                           |

| 56          | D12            |      |                                                                                                                           |

| 57          | D11            |      | , , , , , , , , , , , , , , , , , , ,                                                                                     |

| 58          | D10            |      | the Watchdog timeout is reset.                                                                                            |

| 60          | D9             |      | the RESCON register when RST_n goes from low to high and                                                                  |

| 61          | D8             | I/O  | condition and this bus can also be used to load system configuration information (with pull-up or pull-low resistor) into |

| 87          | D7             |      | The D bus is in a floating state during a bus hold or reset                                                               |

| 88          | D6             |      |                                                                                                                           |

| 89          | D5             |      | Data bus for memory or I/O access.                                                                                        |

| 90          | D4             |      |                                                                                                                           |

| 92          | D3             |      |                                                                                                                           |

| 93          | D2             |      |                                                                                                                           |

| 94          | D1             |      |                                                                                                                           |

| 95          | D0             |      |                                                                                                                           |

| 79          | A0/MA0         |      |                                                                                                                           |

| 78          | A1/MA1         |      |                                                                                                                           |

| 77          | A2/MA2         |      |                                                                                                                           |

| 76          | A3/MA3         |      |                                                                                                                           |

| 72          | A4MA4          |      | MA [10:0]: The SDRAM raw and column address output.                                                                       |

| 71          | A5/MA5         |      | MA [10:0]: The SDRAM row and column address subsuit                                                                       |

| 70          | A6/MA6         |      | on the trailing edge of ALE.                                                                                              |

| 69          | A7/MA7         |      | address output on the D bus. Address is guaranteed to be valid                                                            |

| 68          | A8/MA8         |      | ALE: Address latch enable. Active high. This pin indicates an                                                             |

| 67          | A9/MA9         | "0   |                                                                                                                           |

| 80          | A10/MA10       | I/O  | SAD [7:0]: The combination pins with addresses and data. They are designed for slower peripheral bus.                     |

| 66          | A11/SAD0       |      | SAD [7:0]: The combination pipe with addresses and date. They                                                             |

| 51          | A12/SAD1       |      | hold or reset.                                                                                                            |

| 50          | A13/SAD2       |      | bus. The address bus is in a high-impedance state during a bus                                                            |

| 49          | A14/SAD3       |      | address bus is one-half of a SD_CLK period earlier than the D                                                             |

| 48          | A15/SAD4       |      | Address bus. Non-multiplexed memory or I/O addresses. The                                                                 |

| 47          | A16/SAD5       |      |                                                                                                                           |

| 46          | A17/ PIO7/SAD6 |      |                                                                                                                           |

| 44          | A18/PIO8/SAD7  |      |                                                                                                                           |

| 43          | A19/PIO9/ALE   |      |                                                                                                                           |

|     | • • • •     |         | •                                                                                                                                                                                                                                                                                                                                                                                            |

|-----|-------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

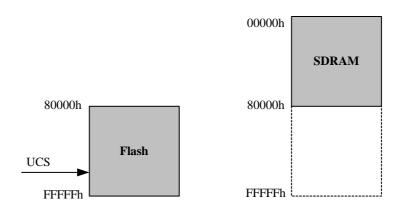

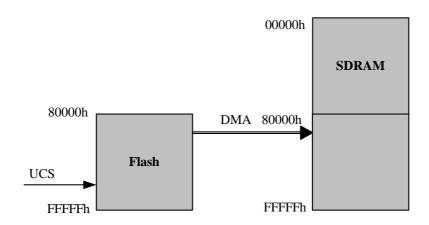

| 96  | UCS_n       | O/PU    | Upper memory chip select. For UCS_n, this pin is active low<br>when the system accesses the defined portion of memory block<br>for the upper 512K bytes (80000h-FFFFh) memory region.<br>UCS_n defaulted active address region is from F0000h to<br>FFFFFh after power-on reset. The address range for UCS_n is<br>programmed by software. This pin incorporates a weak pull-up<br>resistor. |

| 124 | PCS5_n/PIO3 | I/O/PU* | Peripheral chip selects/latched address bit. For PCS_n feature, these pins are active low when the micro-controller accesses the fifth or sixth region of the peripheral memory (I/O or memory space). The base address of PCS n is programmable. These                                                                                                                                      |

| PIN No.                          | Symbol                                            | Туре    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|----------------------------------|---------------------------------------------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Interrupt Control Unit Interface |                                                   |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| 34<br>35                         | PCS2_n/PIO25/IOR_n<br>PCS3_n <b>/</b> PIO26/IOW_n | I/O/PU* | Peripheral chip selects. These pins are active low when the microcontroller accesses the defined peripheral memory block (I/O or memory address). For I/O access, the base address can be programmed in the region from 00000h to 0FFFFh. For memory address access, the base address can be located in the 1M-Byte memory address region. These pins are asserted with the multiplexed D address bus and do not float during bus holds.<br>When register FFEAh bit6 is set, PIN34 is IOR_n and PIN35 is IOW_n.<br>IOR_n/IOW_n are for PCMCIA bus. |  |

| 125<br>126                       | PCS1_n/PIO15<br>PCS0_n/PIO14                      | I/O/PU* | float during bus hold conditions.<br>Peripheral chip selects. These pins are active low when the microcontroller accesses the defined peripheral memory block (I/O or memory address). For I/O access, the base address can be programmed in the region from 00000h to 0FFFh. For memory address access, the base address can be located in the 1M-Byte memory address region. These pins are asserted with the multiplexed D address bus and do not float during bus holds.                                                                       |  |

|                                  |                                                   |         | pins are asserted with the multiplexed D address bus and do not                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| PIN No.     | Symbol             | Туре    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------|--------------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4           | NMI                | I/PD    | Nonmaskable Interrupt. The NMI is the highest priority hardware<br>interrupt and is nonmaskable. When this pin is asserted (NMI<br>transition from low to high), the microcontroller always transfers<br>the address bus to the location specified by the nonmaskable<br>interrupt vector in the micro controller interrupt vector table. The<br>NMI pin must be asserted for at least one SD_CLK period to<br>guarantee that the interrupt is recognized. |

| 5           | INT2/PIO31         | I/O/PU* | Maskable Interrupt Request 2.<br>INT2, it's active high. The interrupt input can be configured to be<br>either edge-triggered or level-triggered. The requesting device<br>must hold the INT2 until the request is acknowledged to<br>guarantee interrupt recognition.                                                                                                                                                                                     |

| 6           | INT1               | I/PD    | Maskable Interrupt Request 1.<br>INT1, except the differences in the interrupt line and interrupt<br>address vector, the function of INT1 is the same as that of INT2.                                                                                                                                                                                                                                                                                     |

| 8           | INTO               | I/PD    | Maskable interrupt request 0.<br>INT0, except the differences in the interrupt line and interrupt<br>address vector, the function of INT0 is the same as that of INT2.                                                                                                                                                                                                                                                                                     |

| Timer Conti | rol Unit Interface |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| PIN No.     | Symbol             | Туре    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 0           |                    |         | Timer input. These pins can be used as clock or control signal input, depending upon the programmed timer mode. After                                                                                                                                                                                                                                                                                                                                      |

| 11<br>12    | TMROUT1/PIO1<br>TMROUT0/PIO10      | I/O/PD* | Timer output. Depending on timer mode select. These pins<br>provide single pulse or continuous waveform. The duty cycle of<br>the waveform is programmable. These pins are floated during a<br>bus hold or reset.                                                                                                                                                                                                                                                                                                                                                                      |

|-------------|------------------------------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DMA Unit In | terface                            |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 13<br>14    | DRQ1/INT6/PIO13<br>DRQ0/INT5/PIO12 | I/O/PU* | DMA request. These pins are asserted high by an external device when the device is ready for DMA channel 1 or channel 0 to perform a transfer. These pins are level-triggered and internally synchronized. The DRQ signals are not latched and must remain active until serviced.<br>For INT6/INT5: When the DMA function is not used, the INT6 and INT5 can be used as an additional external interrupt request. And they share the corresponding interrupt type and register control bits. The INT6/5 are level-triggered only and must be held until the interrupt is acknowledged. |

#### 16550 UART

| PIN No. | Symbol       | Туре   | Description                                                                                                                                                                                                       |

|---------|--------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15      | SIN0/SAD14   | I/O/PU | SIN0: Serial Input. Serial Data Input from the communications<br>link.<br>SAD14: The combination pin with Address and Data. It is for<br>slower device bus.                                                       |

| 16      | SOUT0/SAD13  | I/O/PU | SOUT0: Serial Output. Composite serial data output to the communications link.<br>SAD13: The combination pin with Address and Data. It is for slower device bus.                                                  |

| 17      | RTS0_n/SAD9  | I/O/PU | RTS0_n: Request To Send. When low, this indicates to MODEM or data set that URAT is ready to exchange data. SAD9: The combination pin with Address and Data. It is for slower device bus.                         |

| 19      | DTR0_n/SAD12 | I/O/PU | DTR0_n: Data Terminal Ready. When low, this informs the MODEM or data set that UART is ready to establish a communication link.<br>SAD12: The combination pin with Address and Data. It is for slower device bus. |

| 20      | CTS0_n/SAD8  | I/O/PU | CTS0_n: Clear To Send. When low, this indicates to UART that MODEM or data set is ready to exchange data. SAD8: The combination pin with Address and Data. It is for slower device bus.                           |

| 21      | DSR0_n/SAD11 | I/O/PU | DSR0_n: Data Set Ready. When low, this indicates that MODEM or data set is ready to establish the communication link with UART.<br>SAD11: The combination pin with Address and Data. It is for slower device bus. |

| 22      | DCD0_n/SAD15 | I/O/PU | DCD0_n: Data Carry Detection. When low, it indicates that the data carrier has been detected by the MODEM or data set. SAD15: The combination pin with Address and Data. It is for slower device bus.             |

| 24      | RI0_n /SAD10 | I/O/PU | RI0_n: Ring Indicator. This indicates that a telephone ringing signal has been received by the MODEM or data set.                                                                                                 |

|    |               |        | SAD10: The combination pin with Address and Data. It is for slower device bus.                                                                                                                                                                                                                               |  |  |

|----|---------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 25 | SIN1          | I      | SIN1: Serial Data Input.                                                                                                                                                                                                                                                                                     |  |  |

| 26 | SOUT1         | O/UP   | SOUT1: Serial Data Output. This pin cannot be pulled low.                                                                                                                                                                                                                                                    |  |  |

| 27 | RTS1_n/TDO    | 0      | RTS1_n: Request To Send.<br>TDO: JTAG test data output pin                                                                                                                                                                                                                                                   |  |  |

| 28 | DTR1_n/SBWSEL | I/O/PU | DTR1_n: Data Terminal Ready.<br>SBWSEL is to decide the SAD bus width when the RST_n pin<br>goes from low to high. If SBWSEL is with a pull-low resistor<br>(4.7k ohm), the SAD bus width is 8 bits and 16550's Port 0 is<br>active. Otherwise the SAD bus width is 16 bits and 16550 Port 0<br>is inactive. |  |  |

| 29 | CTS1_n/TMS    | I/PU   | CTS1_n: Clear To Send.<br>JTAG Test mode select pin                                                                                                                                                                                                                                                          |  |  |

| 30 | DSR1_n/TCK    | I/PU   | DSR1_n: Data Set Ready.<br>TCK: JTAG test clock input pin                                                                                                                                                                                                                                                    |  |  |

| 31 | DCD1_n/TDI    | I/PU   | DCD1_n: Carry Sense Detection.<br>TDI: JTAG test data input pin                                                                                                                                                                                                                                              |  |  |

#### **MII Interface**

| PIN No.                  | Symbol                               | Туре   | Description                                                                                                                                                                                                                                                                                                              |

|--------------------------|--------------------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 116<br>112               | TXD1_3/PDIVD0<br>TXD1_0/PFEREQ0      | I/O/PU | Four parallel transmit data lines. This data is synchronized to the assertion of the TXC signal and is latched by the external PHY on the rising edge of the TXC signal.                                                                                                                                                 |

| 115<br>114               | TXD1_2/PDIVD1<br>TXD1_1/PDIVD2       | I/O/PD | PDIVD [2:0] & PFEREQ [0] are hardware configured pins during<br>reset for Multiple PLL. (See chapter.5)<br>PDIVD [2:0]: Multiple selection.<br>PFEREQ [0]: Input clock range selection.                                                                                                                                  |

| 117                      | TXEN1/CLKJMP                         | I/O/PD | This pin functions as transmit enable. It indicates that a transmission is active on the MII port to an external PHY device. CLKJMP: It is a hardware-configured pin, used to select the CLKOUTA output from internal Multiple PLL or X1. When high, the CLKOUTA is from Multiple-PLL. When low, the CLKOUTA is from X1. |

| 111                      | TXC1                                 | I/PD   | Supports the transmit clock supplied by the external PMD device. This clock should always be active.                                                                                                                                                                                                                     |

| 110                      | RXC1                                 | I/PD   | Supports the receive clock supplied by the external PMD device.<br>This clock should always be active.                                                                                                                                                                                                                   |

| 109<br>108<br>107<br>106 | RXD1_3<br>RXD1_2<br>RXD1_1<br>RXD1_0 | I/PD   | Four parallel receive data lines. This data is driven by an external PHY that the media is attached and should be synchronized with the RXC signal.                                                                                                                                                                      |

| 105                      | RXDV1                                | I/PD   | Data valid is asserted by an external PHY when the received data is present on the RXD1 [3:0] lines and is de-asserted at the                                                                                                                                                                                            |

|     |          |        | end of the packet.                                                                                                                                    |

|-----|----------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| 104 | RXER1    | I/PD   | Receiver error shall be asserted to indicate to MAC that an error was detected. This signal should be synchronized with the RXC signal.               |

| 118 | COL1     | I/PD   | This pin functions as the collision detection. When the external physical layer protocol (PHY) device detects a collision, it asserts this pin.       |

| 103 | MDC1     | 0      | MII management data clock is sourced by the R1610C to the external PHY devices as a timing reference for the information transfer on the MDIO signal. |

| 102 | MDIO1    | I/O/PD | MII management data input/output transfers control information and status between the external PHY and the R1610C.                                    |

| 119 | PHY_CHG1 | I/O/PD | To indicate PHY status changed.                                                                                                                       |

## JTAG /SCAN Chain Enable Pin

| PIN No. | Symbol | Туре   | Description                                               |

|---------|--------|--------|-----------------------------------------------------------|

| 32      | JTAGEN | I/O/PD | JTAG function enable. Default is pulled low and disabled. |

| 33      | NC     |        | Not connected                                             |

#### **SDRAM** Interface

| PIN No. | Symbol | Туре | Description                                                                                                                                                                          |  |  |  |

|---------|--------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 74      | SD_CLK | Ο    | SDRAM clock ouput. This clock output is from internal De-skew PLL. It can be one to four multiple of input clock X1, depending on the setting of PDIVD [2:0] during power-on resets. |  |  |  |

| 85      | WE_n   | 0    | SDRAM write enable.                                                                                                                                                                  |  |  |  |

| 84      | CAS_n  | 0    | SDRAM column address selector.                                                                                                                                                       |  |  |  |

| 82      | RAS_n  | 0    | SDRAM raw address selector.                                                                                                                                                          |  |  |  |

| 86      | DQML   | 0    | Input/Output mask.                                                                                                                                                                   |  |  |  |

| 64      | DQMH   | 0    | Input/Output mask.                                                                                                                                                                   |  |  |  |

### **GPIO** Interface

| PIN No. | Symbol       | Туре    | Description                                                                    |  |  |

|---------|--------------|---------|--------------------------------------------------------------------------------|--|--|

| 39      | PIO27        | I/O/PU* | /O/PU* General purpose PIN.                                                    |  |  |

| 41      | PIO28        | I/O/PU* | General purpose PIN.                                                           |  |  |

| 42      | PIO29/UARTX0 | I/O/PD* | General purpose PIN.<br>UARTX0: URAT0 transmission indication for observation. |  |  |

#### Power PINs

| PIN No.                   | Symbol | Туре | Description                        |  |  |  |

|---------------------------|--------|------|------------------------------------|--|--|--|

| 18,45,65,75,<br>91,99,123 | VDDIO  | Ι    | I/O power pin, pure 3.3V.          |  |  |  |

| 1,36,55,73,<br>81,98,113  | VSSIO  | Ι    | I/O ground pin.                    |  |  |  |

| 23,59,97,<br>121          | VDDC   | Ι    | Core power pin, pure 2.5V.         |  |  |  |

| 7,40,83,101               | VSSC   | Ι    | Core ground pin.                   |  |  |  |

| 63                        | VDDP1  | I    | De-skew PLL power pin, pure 2.5V.  |  |  |  |

| 62                        | VSSP1  | I    | De-skew PLL ground pin.            |  |  |  |

| 3                         | VDDP2  | I    | Multiple PLL power pin, pure 2.5V. |  |  |  |

| 2                         | VSSP2  | Ι    | Multiple PLL ground pin.           |  |  |  |

#### Notes:

- 1. When the PIO Data register is enabled, the 18 MUX definition pins can be used as a PIO pin. For example, the PIO29/UARTX0 (Pin 42) can be used as a PIO29 when the PIO Data register is enabled.

- 2. The PIO status during Power-On reset:

- (1) PIO1 and PIO10 are inputs with pull-down.

- (2) PIO7 and PIO9 are normal operations.

- (3) Other PIOs are inputs with pull-up.

- 3. In Slow Bus Mode (Bus Mode 0):

I/O bus is mapped to SAD [15:0] or SAD [7:0]. It depends on the hardware setting of DTR1\_n/SBWSEL Pin (Pin 28) during power-on reset to select 16-bit mode or 8-bit mode.

Memory bus is mapped to A [10:0]/D [15:0].

4. In Normal Bus Mode (Bus Mode 1):

I/O bus and Memory bus are all mapped to A [19:0] and D [15:0]. The SAD [15:0] bus is inactive in this mode.

5. Change Bus Mode 0 and Bus Mode 1 by means of setting the internal Bus Control Register. This action must be initialized by software.

## 3.3 PIN Capacitance Description

| Symbol           | Parameter                       | Min. | Тур. | Max. | Unit |

|------------------|---------------------------------|------|------|------|------|

| C <sub>IN</sub>  | 3.3V Input Capacitance          |      | 2.8  |      | pF   |

| Cout             | 3.3V Output Capacitance         | 2.7  |      | 4.9  | рF   |

| C <sub>BID</sub> | 3.3V Bi-directional Capacitance | 2.7  |      | 4.9  | рF   |

#### 3.4 PIN Pull-up/Pull-down Description

| PIN Name                                                                                                                 | Pin No.                                                   | Pull-up                                                                              | Pull-down                                      | Schmitt<br>Trigger                        | 5V I/O<br>Tolerant | Description                                                                                                                                                                                                                  |

|--------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|--------------------------------------------------------------------------------------|------------------------------------------------|-------------------------------------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RST_n<br>ARDY                                                                                                            | 120<br>122                                                | 1                                                                                    | 0                                              | 1                                         | 1                  |                                                                                                                                                                                                                              |

| NMI<br>INTO<br>INT1                                                                                                      | 4<br>8<br>9                                               | 0                                                                                    | 1                                              | 0                                         | 1                  |                                                                                                                                                                                                                              |

| WR_n/BWSEL                                                                                                               | 38                                                        | 1                                                                                    | 0                                              | 0                                         | 1                  |                                                                                                                                                                                                                              |

| TMROUT0<br>TMROUT1<br>/PIO                                                                                               | 12<br>11                                                  | 0                                                                                    | PIO10<br>PIO1                                  | 0                                         | 1                  | When set in normal operation, these<br>two pins are with neither pull-up nor<br>pull-down resistors. However, when<br>set in PIO, they are input with<br>pull-down resistors.                                                |

| UCS_n                                                                                                                    | 96                                                        | 1                                                                                    | 0                                              | 1                                         | 0                  |                                                                                                                                                                                                                              |

| PIO27<br>PIO28                                                                                                           | 39<br>41                                                  | PIO27<br>PIO28                                                                       | 0                                              | 0                                         | 1                  |                                                                                                                                                                                                                              |

| PIO29/UARTX0                                                                                                             | 42                                                        | 0                                                                                    | PIO29                                          | 0                                         | 1                  |                                                                                                                                                                                                                              |

| INT2<br>PCS0_n<br>PCS1_n<br>PCS2_n/IOR_n<br>PCS3_n/IOW_n<br>PCS5_n<br>TMRIN0<br>TMRIN1<br>DRQ0/INT5<br>DRQ1/INT6<br>/PIO | 5<br>126<br>125<br>34<br>35<br>124<br>10<br>9<br>14<br>13 | PIO31<br>PIO14<br>PIO15<br>PIO25<br>PIO26<br>PIO3<br>PIO11<br>PIO0<br>PIO12<br>PIO13 | 0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 | 0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 | 1                  | When set in normal operation, these<br>pins are with neither pull-up nor<br>pull-down resistors. However, when<br>set in PIO, they are input with<br>pull-up, pull-down, or schimitt trigger<br>as listed in the left table. |

| DCD0_n<br>SIN0<br>SOUT0<br>DTR0_n<br>DSR0_n<br>RI0_n<br>RTS0_n<br>CTS0_n<br>/SAD15-8                                     | 22<br>15<br>16<br>19<br>21<br>24<br>17<br>20              | 1                                                                                    | 0                                              | 0                                         | 1                  |                                                                                                                                                                                                                              |

# R1610C

### Fast Ethernet RISC Processor

| SOUT1                                                          | 26                                            |   |   |   |   |  |

|----------------------------------------------------------------|-----------------------------------------------|---|---|---|---|--|

| DSR1_n/TCK                                                     | 30                                            | 1 | 0 | 0 | 1 |  |

| DCD1_n/TDI<br>CTS1_n/TMS                                       | 31<br>29                                      |   |   |   |   |  |

|                                                                |                                               |   |   |   |   |  |

| DTR1_n/SBWSEL                                                  | 28                                            | 1 | 0 | 0 | 1 |  |

| TXC1<br>RXC1                                                   | 111<br>110                                    | 0 | 1 | 1 | 1 |  |

| RXD1_3<br>RXD1_2<br>RXD1_1<br>RXD1_0<br>RXDV1<br>RXER1<br>COL1 | 109<br>108<br>107<br>106<br>105<br>104<br>118 | 0 | 1 | 0 | 1 |  |

| TXD1_3/PDIVID0<br>TXD1_0/PFREQ0                                | 116<br>112                                    | 1 | 0 | 0 | 1 |  |

| TXD1_2/PDIVID1<br>TXD1_1/PDIVID2<br>TXEN1/CLKJMP               | 115<br>114<br>117                             | 0 | 1 | 0 | 1 |  |

| MDIO1                                                          | 102                                           | 0 | 1 | 0 | 1 |  |

| JTAGEN                                                         | 32                                            | 0 | 1 | 1 | 1 |  |

| PHY_CHG1                                                       | 119                                           | 0 | 1 | 0 | 1 |  |

| CLKOUTA                                                        | 100                                           | 0 | 0 | 0 | 0 |  |

| RD_n                                                           | 37                                            | 0 | 0 | 0 | 1 |  |

| <br>A[17:19]/PIO                                               | 43,44,4<br>6                                  | 0 | 0 | 0 | 0 |  |

| A[0:10]                                                        | 67~72<br>76~80                                | 0 | 0 | 0 | 0 |  |

| A[11:16]                                                       | 47~51<br>66                                   | 0 | 0 | 0 | 0 |  |

| D[0:15]                                                        | 52~54<br>56~58<br>60~61<br>87~90<br>92~95     | 0 | 0 | 0 | 0 |  |

| SIN1                                                           | 25                                            | 0 | 0 | 0 | 1 |  |

| RTS1_n/TDO                                                     | 27                                            | 0 | 0 | 0 | 1 |  |

| MDC1                                                           | 103                                           | 0 | 0 | 0 | 0 |  |

| SD_CLK                                                         | 74                                            | 0 | 0 | 0 | 0 |  |

| WE_n<br>CAS_n<br>RAS_N<br>DQML<br>DQMH                         | 85<br>84<br>82<br>86<br>64                    | 0 | 0 | 0 | 0 |  |

Note: The pins never in the pull-up, pull-down, schimitt trigger, and I/O pad status are not shown in the above table.

## 4. Oscillator Characteristics

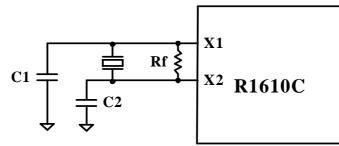

## 4.1 Fundamental Mode

- C1 ----- 20pF  $\pm$  20%

- C2 ----- 20pF  $\pm$  20%

Rf ----- 1 mega-ohm

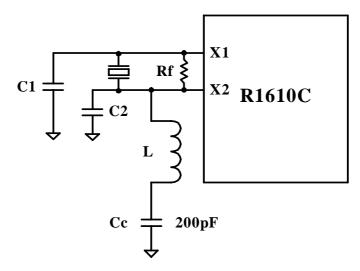

#### 4.2 Third-Overtone Mode

Normally, high frequency use for third overtone mode can get price advantage, but additional L and Cc are needed.

Typical value suggestions are as follows:

- C1 -----  $20pF \pm 20\%$

- C2 ----- 20pF ± 20%

- Cc ----- 200pF± 20%

- Rf ----- 1 Mega-Ohm

- L ------ 4.7uH, 6.8uH, 8.2uH, 10uH (25MHz)

Note: X1 input clock must be within + - 100ppm tolerance.

# 5. Clock Unit

#### PLL Configuration Table:

| Input Clock<br>Range (Mhz) | PFEREQ[0] | PD | PDIVD[2:0] |   | PDIVD[2:0] Mult |          | Multiple | Output Clock<br>(Mhz) |

|----------------------------|-----------|----|------------|---|-----------------|----------|----------|-----------------------|

|                            |           | 0  | 0          | 0 | 1               | Reserved |          |                       |

|                            |           | 0  | 0          | 1 | 2               | 50       |          |                       |

|                            |           | 0  | 1          | 0 | 3               | 75       |          |                       |

| 25                         | 1         | 0  | 1          | 1 | 4               | 100      |          |                       |

| 25                         | 1         | 1  | 0          | 0 |                 | Reserved |          |                       |

|                            |           | 1  | 0          | 1 |                 | Reserved |          |                       |

|                            |           | 1  | 1          | 0 |                 | Reserved |          |                       |

|                            |           | 1  | 1          | 1 |                 | Reserved |          |                       |

|                            |           | 0  | 0          | 0 | 1               | 40       |          |                       |

|                            |           | 0  | 0          | 1 | 2               | 80       |          |                       |

|                            |           | 0  | 1          | 0 |                 | Reserved |          |                       |

| 40                         | 0         | 0  | 1          | 1 |                 | Reserved |          |                       |

| 40                         | 0         | 1  | 0          | 0 |                 | Reserved |          |                       |

|                            |           | 1  | 0          | 1 |                 | Reserved |          |                       |

|                            |           | 1  | 1          | 0 |                 | Reserved |          |                       |

|                            |           | 1  | 1          | 1 |                 | Reserved |          |                       |

For example: If input clock =25 Mhz, then set PFEREQ=1b.

If PDIVD[2:0]=000b, then PLL output clock =25 Mhz If PDIVD[2:0]=011b, then PLL output clock =100 Mhz

# 6. Execution UNIT

#### 6.1 General Registers

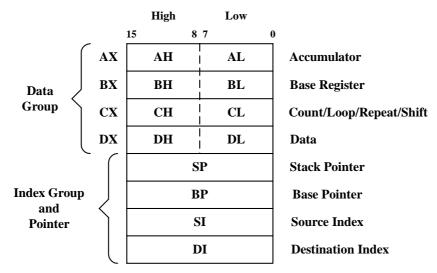

The R1610C has eight 16-bit general registers. And the AX, BX, CX, and DX can be subdivided into two 8-bit registers (AH, AL, BH, BL, CH, CL, DH, and DL). The functions of these registers are described as follows:

AX: Word Divide, Word Multiply, Word I/O operation.

AH: Byte Divide, Byte Multiply, Byte I/O, Decimal Arithmetic, Translate operation.

AL: Byte Divide, Byte Multiply operation.

BX: Translate operation.

CX: Loops, String operation

CL: Variable Shift and Rotate operation.

DX: Word Divide, Word Multiply, Indirect I/O operation

SP: Stack operations (POP, POPA, POPF, PUSH, PUSHA, PUSHF)

BP: General-purpose registers which can be used to determine offset address of operands in Memory.

SI: String operations

DI: String operations

**GENERAL REGISTERS**

#### 6.2 Segment Registers

R1610C has four 16-bit segment registers: CS, DS, SS, and ES. The segment registers contain the base addresses (starting location) of these memory segments, and they are immediately addressable for code (CS), data (DS & ES), and stack (SS) memory.

**CS (Code Segment)**: The CS register points to the current code segment, which contains instruction to be fetched. The default location memory space for all instructions is 64K. The initial value of CS register is 0FFFFh.

**DS (Data Segment)**: The DS register points to the current data segment, which generally contains program variables. The DS register is initialized to 0000H.

**SS (Stack Segment)**: The SS register points to the current stack segment, which is for all stack operations, such as pushes and pops. The stack segment is used for temporary space. The SS register is initialized to 0000H.

**ES (Extra Segment)**: The ES register points to the current extra segment, which is typically for data storage, such as large string operations and large data structures. The ES register is initialized to 0000H.

| 15 | 8 7 | 0             |

|----|-----|---------------|

|    | CS  | Code Segment  |

|    | DS  | Data Segment  |

|    | SS  | Stack Segment |

|    | ES  | Extra Segment |

#### **SEGMENT REGISTERS**

#### 6.3 Instruction Pointer and Status Flags Registers

**IP (Instruction Pointer):** The IP is a 16-bit register and it contains the offset of the next instruction to be fetched. The IP register cannot be directly accessed by software, but can be updated by the bus interface unit. It can be changed, saved or restored as a result of program execution. The IP register is initialized to 0000H and the starting execution address for CS:IP is at 0FFFF0H.

| -  |      |      | Proce<br>0000ł | Processor Status Flags Register<br>0000h |    |    |    |    |    |      |    |      |    |      |    |

|----|------|------|----------------|------------------------------------------|----|----|----|----|----|------|----|------|----|------|----|

| 15 | 14   | 13   | 12             | 11                                       | 10 | 9  | 8  | 7  | 6  | 5    | 4  | 3    | 2  | 1    | 0  |

|    | Rese | rved |                | OF                                       | DF | IF | TF | SF | ZF | Rsvd | AF | Rsvd | PF | Rsvd | CF |

These flags reflect the status after the Execution Unit is executed.

| Bit   | Name | Description                                                                                                                                                                                                                                                                |

|-------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15-12 | Rsvd | Reserved.                                                                                                                                                                                                                                                                  |

| 11    | OF   | Overflow Flag. If an arithmetic overflow occurs, this flag will be set.                                                                                                                                                                                                    |

| 10    | DF   | Direction Flag. If this flag is set, the string instructions are in the process of incrementing address. If DF is cleared, the string instructions are in the process of decrementing address. Refer to the STD and CLD instructions for how to set and clear the DF flag. |

| 9     |      | Interrupt-Enable Flag. Refer to the STI and CLI instructions for how to set and clear the IF flag.<br>Set to 1: The CPU enables the maskable interrupt request.<br>Set to 0: The CPU disables the maskable interrupt request.                                              |

| D | R |                        |

|---|---|------------------------|

| R |   | RISC DSP Communication |

| 8 |      | Trace Flag. Set to enable single-step mode for debugging; Clear to disable the single-step mode.<br>If an application program sets the TF flag with POPF or IRET instruction, a debug exception is<br>generated after the instruction (The CPU automatically generates an interrupt after each<br>instruction) that follows the POPF or IRET instruction. |

|---|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7 | SF   | Sign Flag. If this flag is set, the high-order bit of the result of an operation will be 1, indicating the state of being negative.                                                                                                                                                                                                                       |

| 6 | ZF   | Zero Flag. If this flag is set, the result of operation will be zero.                                                                                                                                                                                                                                                                                     |

| 5 | Rsvd | Reserved                                                                                                                                                                                                                                                                                                                                                  |

| 4 | AF   | Auxiliary Flag. If this flag is set, there will be a carry from the low nibble to the high one or a borrow from the high nibble to the low nibble of the AL general-purpose register. It is used in BCD operation.                                                                                                                                        |

| 3 | Rsvd | Reserved                                                                                                                                                                                                                                                                                                                                                  |

| 2 | PF   | This flag will be set if the result of the low-order 8 bits operation has even parity.                                                                                                                                                                                                                                                                    |

| 1 | Rsvd | Reserved                                                                                                                                                                                                                                                                                                                                                  |

| 0 | CF   | Carry Flag. If CF is set, there will be a carry out or a borrow into the high-order bit of the instruction result.                                                                                                                                                                                                                                        |

#### 6.4 Address Generation

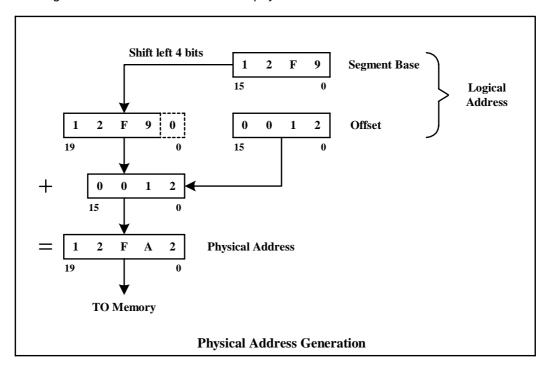

The Execution Unit generates a 20-bit physical address to Bus Interface Unit by the Address Generation. Memory is organized in sets of segments. Each segment contains a 16-bit value. Memory is addressed with a two-component address that consists of a 16-bit segment and 16-bit offset. The Physical Address Generation figure describes how the logical address is transferred to the physical address.

# 7. Peripheral Register List

**RISC DSP Communication**

**RDC**<sup>®</sup>

The Peripheral Control Block can be mapped into either Memory or I/O space by programming the Peripheral Control Block Relocation Register (FEh). After reset, the default Legacy Peripheral Control Block offset is located at FF00h in I/O space, the SDRAM Control Register is located at FE00h in I/O space, and Ethernet Control Register is located at FD00h and FE00h in I/O space.

The following table lists are all the definitions of the Peripheral Control Block Registers, and the detailed descriptions will be arranged on the related Block Unit.

#### 7.1 Legacy Peripheral Registers (Base Address FF00h)

| Offset<br>(HEX) | Register Name                                   | Page | Offset<br>(HEX) | Register Name                            | Page |

|-----------------|-------------------------------------------------|------|-----------------|------------------------------------------|------|

| FE              | Peripheral Control Block Relocation<br>Register | 28   | 70              | PIO Mode 0 Register                      | 90   |

| F8              | Processor Extended ID Register                  | 29   | 66              | Timer 2 Mode/Control Register            | 69   |

| F6              | Reset Configuration Register                    | 31   | 62              | Timer 2 Maxcount Compare A Register      | 70   |

| F4              | Processor Release Level Register                | 28   | 60              | Timer 2 Count Register                   | 70   |

| F2              | Auxiliary configuration Register                | 37   | 5E              | Timer 1 Mode/Control Register            | 67   |

| EA              | Bus Control Register                            | 34   | 5C              | Timer 1 Maxcount Compare B Register      | 69   |

| E6              | Watchdog Timer Control Register                 | 71   | 5A              | Timer 1 Maxcount Compare A Register      | 68   |

| E4              | Enable RCU Register                             | 43   | 58              | Timer 1 Count Register                   | 68   |

| E2              | Clock Prescaler Register                        | 43   | 56              | Timer 0 Mode/Control Register            | 65   |

| DA              | DMA 1 Control Register                          | 59   | 54              | Timer 0 Maxcount Compare B Register      | 66   |

| D8              | DMA 1 Transfer Count Register                   | 61   | 52              | Timer 0 Maxcount Compare A Register      | 66   |

| D6              | DMA 1 Destination Address High<br>Register      | 61   | 50              | Timer 0 Count Register                   | 66   |

| D4              | DMA 1 Destination Address Low<br>Register       | 61   | 44              | Serial Port 0 interrupt control register | 46   |

| D2              | DMA 1 Source Address High Register              | 62   | 42              | Serial port 1 interrupt control register | 46   |

| D0              | DMA 1 Source Address Low Register               | 62   | 40              | MAC Interrupt Control Register           | 47   |

| CA              | DMA 0 Control Register                          | 57   | 3C              | INT2 Control Register                    | 48   |

| C8              | DMA 0 Transfer Count Register                   | 57   | 3A              | INT1 Control Register                    | 48   |

| C6              | DMA 0 Destination Address High<br>Register      | 58   | 38              | INT0 Control Register                    | 49   |

| C4              | DMA 0 Destination Address Low<br>Register       | 58   | 36              | DMA1/INT6 Interrupt Control Register     | 50   |

| C2              | DMA 0 Source Address High Register              | 58   | 34              | DMA0/INT5 Interrupt Control Register     | 50   |

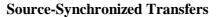

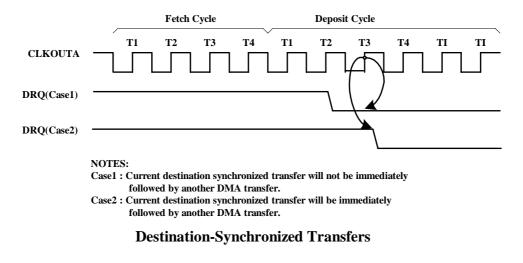

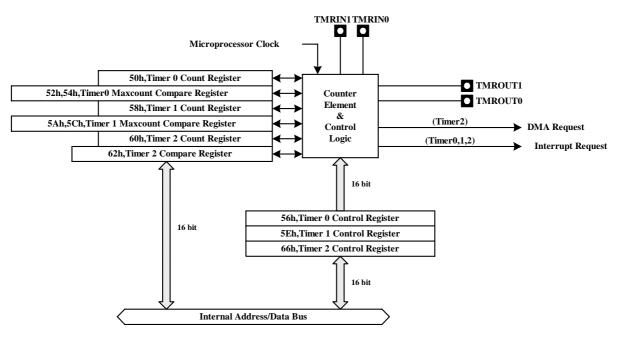

| C0              | DMA 0 Source Address Low Register               | 59   | 32              | Timer Interrupt Control Register         | 51   |